Project

What’s new in SIGN-HEP

- Industrialization focus: upgrade the open design flow into a repeatable, production-minded path for security ICs.

- Hardening & verification at scale: expand side-channel/fault-injection countermeasures and formal checks for real-world robustness.

- Reference designs & demos: deliver an open, industry-aligned HSM/Root-of-Trust reference with clear bring-up guides.

- PDK & MPW continuity: keep leveraging accessible PDKs and shuttle runs to lower the barrier for replication.

- Community & training: docs, tutorials, and hands-on material to help teams reproduce and extend our work.

Built on VE-HEP outcomes

- Silicon-proven baseline: two tapeouts and a working demonstrator established the foundation. → See VE-HEP results

- Open assets: RTL, firmware, and flow instructions remain public and actively maintained.

- Transparent methods: open-source EDA + reproducible steps stay at the core of our approach.

Why it matters

Trust in hardware starts with transparency. SIGN-HEP turns transparent methods into deployable building blocks—so research teams, SMEs, and integrators can evaluate, reproduce, and adopt trustworthy silicon with fewer hurdles.

Presentations, Papers, Flyer, Links

Documents from 2025

- The European Reference Fab - Blueprint for a Trusted and Transparent Manufacturing Network

- Specification of the DI-SIGN-HEP HSM prototype

- Position Paper on Free Open Chip Design

- The Transparent Reference Fab: A scalable, open blueprint for European semiconductor sovereignty @FSiC202

- Break Ground on Open Access to Hardware PUF-based Security IP in Europe

Documents from 2024

Documents from 2023

- Our 2023 press release: DE; EN; JP

- Project presentation at “Day for Trustworthy Electronics”

- Easimask – Towards Efficient, Automated, and Secure Implementation of Masking in Hardware

2023 Design, Automation and Test in Europe Conference (DATE) - Verified Value Chains, Innovation and Competition

Highlights document

2023 IEEE International Conference on Cyber Security and Resilience (CSR)

Documents from 2022

- Open Source Hardware und die Industrie (Englisch, German - original )

Kommentare beim „WebTalk Freie und Open Source Hardware” der Gesellschaft für Informatik - Input zur Designinitiative Mikroelektronik des BMBF

- Motivation for an open EDA Eco System (Video)

- Pitch Talk (flyer)

- Pitch Talk (video)

- Towards a Free and Open EDA Supply Chain (slides)

- Processor Verification (slides)

Requirements Analysis

In the first project phase we worked out the requirements for an open source tool chain to be demonstrated on a hardware security module. The full requirements report can be downloaded here. In its introduction our motivation is described [Requirements Report]

ASIC Design

- FPGA

an FPGA based rapid prototyping platform was developed to shorten the ASIC design time and increase the ASIC quality. The FPGA code can be found on our GitHUb

https://github.com/VE-HEP/VE-HEP-HW-SW - Processor

GDS publication planned

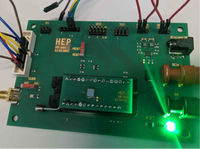

Demonstrator

Information about the Demonstrator will follow shortly. But it is already alive!