Project

The project VE-HEP will show the feasibility of using open-source tools in a wide range of the digital chip design value chain. This includes the use of an open-source processor design, the use of open-source design tools e.g. for the synthesis or the ”place and route”, as well as the development of public available automatic implementation schemes to harden the chip design against hardware attacks. The use case to implement all this ambitious goals is the design and fabrication of an open-source hardware security module (HSM) that will be integrated into an automotive application. To improve the quality and trustworthiness of such a critical module, verification schemes for the different design steps will be developed, extended and integrated into the design flow.

Presentations, Papers, Flyer

Documents from 2023

- Our 2023 press release: DE; EN; JP

- Project presentation at “Day for Trustworthy Electronics”

- Easimask – Towards Efficient, Automated, and Secure Implementation of Masking in Hardware

2023 Design, Automation and Test in Europe Conference (DATE) - Verified Value Chains, Innovation and Competition

Highlights document

2023 IEEE International Conference on Cyber Security and Resilience (CSR)

Documents from 2022

- Open Source Hardware und die Industrie (Englisch, German - original )

Kommentare beim „WebTalk Freie und Open Source Hardware” der Gesellschaft für Informatik - Input zur Designinitiative Mikroelektronik des BMBF

- Motivation for an open EDA Eco System (Video)

- Pitch Talk (flyer)

- Pitch Talk (video)

- Towards a Free and Open EDA Supply Chain (slides)

- Processor Verification (slides)

Requirements Analysis

In the first project phase we worked out the requirements for an open source tool chain to be demonstrated on a hardware security module. The full requirements report can be downloaded here. In its introduction our motivation is described [Requirements Report]

ASIC Design

- FPGA

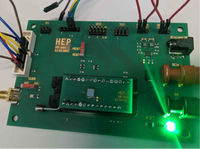

an FPGA based rapid prototyping platform was developed to shorten the ASIC design time and increase the ASIC quality. The FPGA code can be found on our GitHUb

https://github.com/VE-HEP/VE-HEP-HW-SW - Processor

GDS publication planned

Demonstrator

Information about the Demonstrator will follow shortly. But it is already alive!